## Supercapacitor Energy Storage System based on Modular Multilevel Converter with embedded selfbalance control

Doctoral Thesis by

Fernando Dávalos Hernández

Doctoral Program in Engineering Systems

Supervisor Associate Professor Federico Martin Ibañez

Moscow 2023

© Fernando Dávalos Hernández 2023

I hereby declare that the work presented in this thesis was carried out by myself at Skolkovo Institute of Science and Technology, Moscow, except where due acknowledgment is made and has not been submitted for any other degree.

Fernando Dávalos Hernández Associate Prof. Federico Martin Ibañez

#### Abstract

As renewable energy sources interconnected to the grid increase, a viable solution to sustain the stability of the grid is by deploying distributed Energy Storage Systems (ESS) along the grid. For this application, ESSs should be capable of managing high-power ratings in the milliseconds to seconds time range, thus Supercapacitors (SCs) are attractive devices to fulfill this requirement. The research objective is to design an ESS topology that can be expandable and scalable, avoiding the complexity of actual systems by adopting the Modular Multilevel Converter (MMC) approach. For this reason, an important aspect is to enhance the submodules with self-balancing capabilities to accommodate as many SCs as required by the grid application.

MMCs have been deeply studied for high-voltage DC applications, even though an expensive technology, the benefits of implementing them in large-scale projects turn them a viable solution in contrast with traditional AC lines, as they provide a more robust and efficient way to transfer energy over long distances. Few research has been done in low-voltage MMC applications due to the complexity of the controller and the limited benefits in efficiency, but it is an innovative approach to add to each Submodule (SM) an energy storage device to create an ESS. The resulting ESS can scale more quickly as it is possible to just add more SMs to the system in series to increase the voltage or in parallel to increase the power. In addition, with the added capability to self-balance the SCs, a robust ESS can be designed in comparison to traditional ones which require independent

power stages to accomplish the balancing system, the DC/DC converter, and the DC/AC inverter.

This research work covers in detail the design methodology of the proposed MMC-based, simulations validating the proposal and the grid interconnection operation, an optimization methodology for analyzing the efficiency and improving it, and finally two prototypes used to validate the proposed MMC-based ESS. The first lab-scale prototype validates the MMC-based ESS operation, and the second prototype validates the efficiency improvements done based on the optimization methodology, achieving around ~93% efficiency value for a complete low-voltage MMC-based 220V<sub>AC</sub> 16kW ESS.

In line with the mission of the Center of Energy and Technology at Skoltech, this research in energy conversion can provide an efficient MMC-based ESS converter and it can be used to enhance frequency control capabilities of the grid. To conclude, a relevant contribution to the field of low-voltage MMCs was made with this PhD research work.

### **Publications**

- 1. **Hernandez, Fernando Davalos**, Federico Ibanez, Sebastian Gutierrez, and Wilmar Martinez. 2020. "Improvements on Signal-to-Noise Ratio in Feedback Measurement in DC/DC Converters." In 2020 22nd European Conference on Power Electronics and Applications, EPE 2020 ECCE Europe. Institute of Electrical and Electronics Engineers Inc. doi:10.23919/EPE20ECCEEurope43536.2020.9215774.

- 2. **Hernandez, Fernando Davalos**, Federico Ibanez, Rahim Samanbakhsh, and Ramiro Velazquez. 2021. "A Comparative Study of Energy Storage Systems Based on Modular Multilevel Converters." In IECON Proceedings (Industrial Electronics Conference). Vol. 2021-October. IEEE Computer Society. doi:10.1109/IECON48115.2021.9589539.

- 3. **Davalos Hernandez, Fernando**, Rahim Samanbakhsh, Parham Mohammadi, and Federico Martin Ibanez. 2021. "A Dual-Input High-Gain Bidirectional DC/DC Converter for Hybrid Energy Storage Systems in DC Grid Applications." *IEEE Access* 9. Institute of Electrical and Electronics Engineers Inc.: 164006–16. doi:10.1109/ACCESS.2021.3132896.

- 4. **Hernandez, Fernando Davalos**, Rahim Samanbakhsh, Federico Martin Ibanez, and Fernando Martin. 2022. "Self-Balancing Supercapacitor Energy Storage System Based on a Modular Multilevel Converter." *Energies* 15, no. 1: 338. https://doi.org/10.3390/en15010338

## Acknowledgments

To my supervisor who always encouraged me to work beyond the difficulties of the pandemic, for giving me all its expertise in power electronics, and for truthfully believing in my research.

To my wife who was always there to support me and give me strength through the entire PhD.

To my friends from Skoltech, their interesting conversations and ideas inspired me.

To my family for always supporting and encouraging me to pursue greater goals.

# **Table of Contents**

| Abstrac | zt                                                                   | . 3 |

|---------|----------------------------------------------------------------------|-----|

| Publica | tions                                                                | . 5 |

| Acknov  | vledgments                                                           | . 6 |

| 1. In   | ntroduction                                                          | 16  |

| 1.1.    | Why ESSs are needed, application examples                            | 17  |

| 1.2.    | Types of energy storage devices and systems                          | 19  |

| 1.3.    | ESS grid synchronization.                                            | 24  |

| 1.4.    | The basic elements of ESSs                                           | 25  |

| 1.5.    | Objective of the research and structure                              | 28  |

| Chapter | r 2. Literature Review                                               | 30  |

| 2.1.    | High-gain DC/DC converters                                           | 31  |

| 2.2.    | Bidirectional multi-level converters                                 | 37  |

| 2.3.    | MMC-based Energy Storage Systems                                     | 44  |

| 2.4.    | Comparison of MMC-based ESSs (efficiencies, costs, THD, and volum 47 | ıe) |

| Chapter | r 3. Proposed MMC                                                    | 53  |

| 3.1.    | Principle of operation.                                              | 54  |

| 3.1     | .1 Buck-mode ( $V_{SC} \rightarrow V_{O}$ )                          | 56  |

| 3.1     | .2 Boost-mode $(V_O \rightarrow V_{SC})$                             | 64  |

| 3.1     | .3. Small-signal analysis                                            | 67  |

| 3.2.    | Proposed MMC with one SC per SM                                      | 70  |

| 3.2     | 2.1. SM Self-balancing technique                                     | 71  |

| 3.2     | 2.2. General MMC controller                                          | 73  |

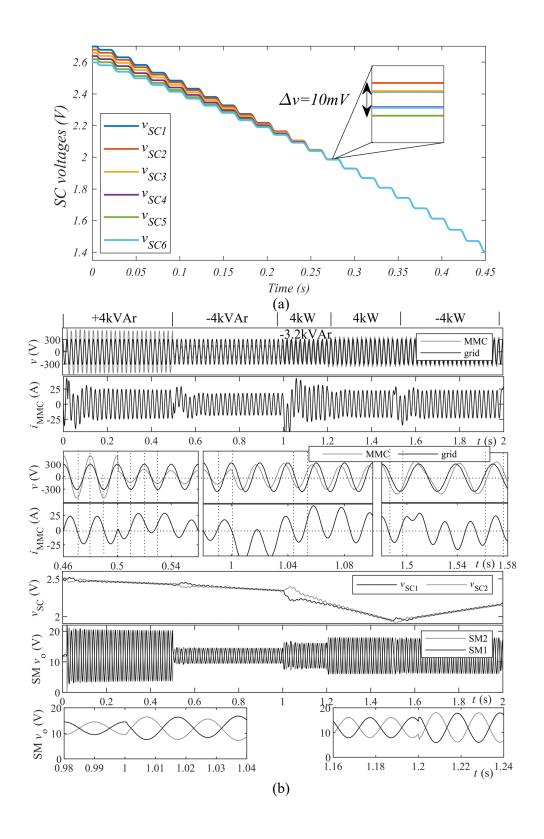

| 3.2.3. Simulation results                                                     | 78 |

|-------------------------------------------------------------------------------|----|

| 3.3. Extension to three-phase system                                          | 82 |

| 3.4. Multiple SCs per SM analysis and formulation                             | 83 |

| 3.4.1. Sensitivity analysis - methodology                                     | 84 |

| 3.4.2. Case study: 3000F SC cell                                              | 89 |

| 3.4.3. Results of the analysis                                                | 92 |

| 3.4.3.1. MMC self-balance and internal BB equalization test                   | 92 |

| 3.4.3.2. SMs' efficiency through the entire discharge                         | 94 |

| 3.4.3.3. MMC overall efficiency.                                              | 97 |

| Chapter 4. Experimental results and validations                               | 01 |

| 4.1. Prototype with a single SC per SM                                        | 01 |

| 4.2. Prototype with 4 SCs per SM obtained after the sensitivity analysis . 10 | 05 |

| Conclusions and future work                                                   | 10 |

| Appendix                                                                      | 13 |

| References                                                                    | 20 |

#### **List of Abbreviations**

AC Alternating Current

BB Buck-Boost

BMS Battery Management System

CAES Compressed Air Energy Storage

CDF Cumulative Distribution Function

DC Direct Current

DSP Digital Signal Processor

DV Deadband

EMS Energy Management System

ESL Equivalent Series Inductance

ESR Equivalent Series Resistance

ESS Energy Storage System

FACTS Flexible AC Transmission Systems

HF High Frequency

HVDC High Voltage Direct-Current

IRENA International Renewable Energy Agency

MCU Microcontroller Unit

MMC Modular Multilevel Converter

PCC Point of Common Coupling

PI Proportional Integral Controller

PLL Phase Locked Loop

PR Proportional Resonant Controller

PV Photovoltaic

PWM Pulse Width Modulation

RC Resistive-Capacitive Load

RL Resistive-Inductive Load

RMS Root Mean Square

SC Supercapacitor

SM Submodule

SMES Superconducting Magnetic Energy Storage

SMS Supercapacitor Management System

SOC State of Charge

STATCOM Static Synchronous Compensator

THD Total Harmonic Distortion

UPS Uninterruptible Power Supply

VDS Drain-Source Voltage

VRE Variable Renewable Energy

ZVS Zero-Voltage Switching

# **List of Figures**

| Fig. 1 IRENA's forecast for fossil-fuel energy demand and CO <sub>2</sub> emissions [1] 16 |

|--------------------------------------------------------------------------------------------|

| Fig. 2 Traditional grid vs. emerging flexible grid [6]                                     |

| Fig. 3 100MW ESS (left) versus 100MW gas turbine (right) [5]                               |

| Fig. 4 Energy density and power density comparison between various energy storage          |

| devices [3]                                                                                |

| Fig. 5 Energy storage devices are ordered based on their power rating and discharging      |

| times, and their possible application in the grid [3]                                      |

| Fig. 6 SC single cell composition.                                                         |

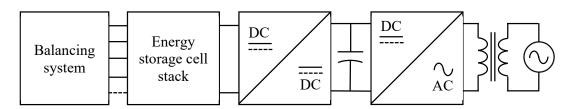

| Fig. 7 ESS basic block diagram                                                             |

| Fig. 8 High-gain bidirectional quadratic DC-DC converter based on coupled inductor         |

| [44]                                                                                       |

| Fig. 9 Wide input range DC/DC converter composed of two cascaded stages [45] 33            |

| Fig. 10 High-gain soft-switching bidirectional DC/DC converter composed of two half-       |

| bridges [46]                                                                               |

| Fig. 11 ZVS bidirectional DC/DC converter with phase-shift plus PWM control scheme         |

| [47]                                                                                       |

| Fig. 12 High-gain dual-input DC/DC converter [48]                                          |

| Fig. 13 Extended range ZVS active-clamped current-fed full-bridge isolated DC/DC           |

| converter [49]                                                                             |

| Fig. 14 Flying-capacitor multi-level DC/DC converter, 3-level example                      |

| Fig. 15 An n-stage switched-capacitor DC/DC converter schematic                            |

| Fig. 16 Multi-level bidirectional DC/DC converter with high efficiency                     |

| Fig. 17 SiC-based high-gain bidirectional DC/DC multi-level resonant converter                                                           | 42   |

|------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 18 (a) Half-bridge with SC connected through an inductor, (b) Half-bridge with                                                      | l    |

| integrated DC/DC boost converter, (c) Soft-switching SM cell, and (d) Alternation                                                        | tive |

| MMC topology to include SCs.                                                                                                             | 47   |

| Fig. 19 MMC-based ESS comparison results for (a) Output voltage and calculated T                                                         | ΉD   |

| and (b) Efficiencies.                                                                                                                    | 49   |

| Fig. 20 ESS basic block diagram.                                                                                                         | 53   |

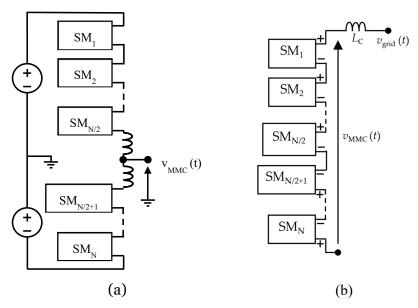

| Fig. 21 Block diagram (a) of the traditional and (b) the proposed MMC topology                                                           | 54   |

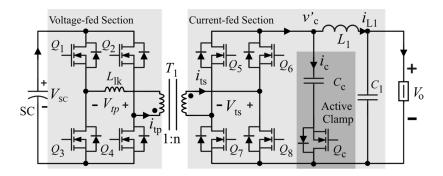

| Fig. 22 Bidirectional full-bridge DC/DC converter, presented in [50]                                                                     | 55   |

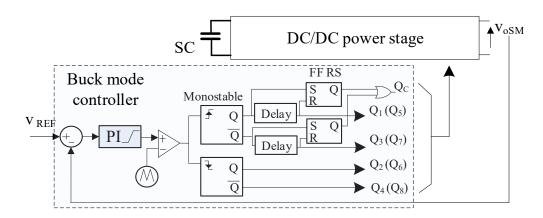

| Fig. 23 Proposed SM Buck-mode controller with gating signals                                                                             | 56   |

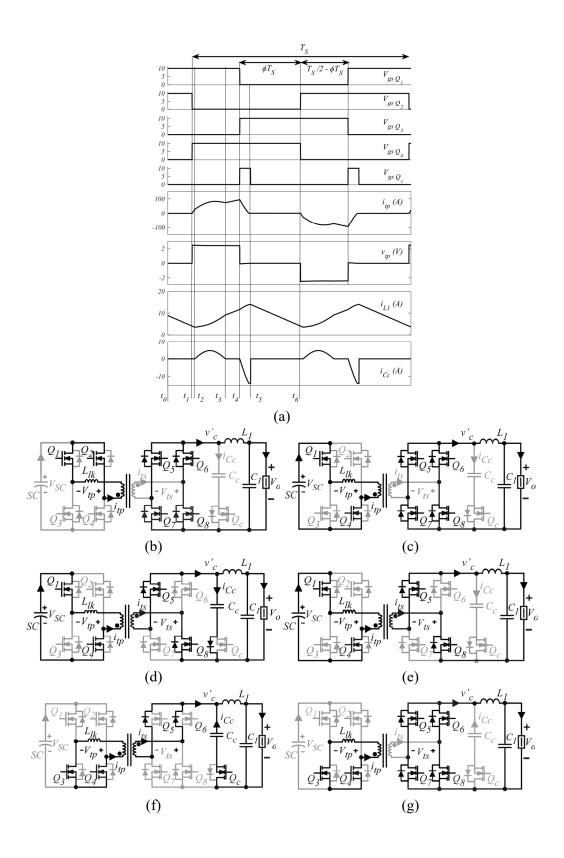

| Fig. 24 Bidirectional full-bridge, (a) waveforms, (b) before 1st interval, (c) 1st interval                                              | al,  |

| (d) 2 <sup>nd</sup> interval, (e) 3 <sup>rd</sup> interval, (f) 4 <sup>th</sup> interval, and (g) 5 <sup>th</sup> interval for the Buck- | -    |

| mode                                                                                                                                     | 58   |

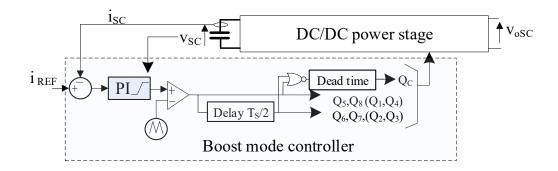

| Fig. 25 Proposed SM Boost-mode controller.                                                                                               | 64   |

| Fig. 26 Bidirectional Full-bridge Boost-mode waveforms.                                                                                  | 65   |

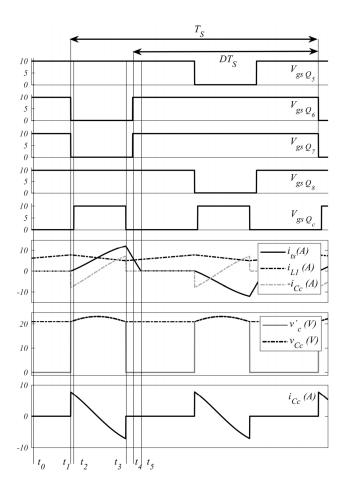

| Fig. 27 SM inner control loop.                                                                                                           | 69   |

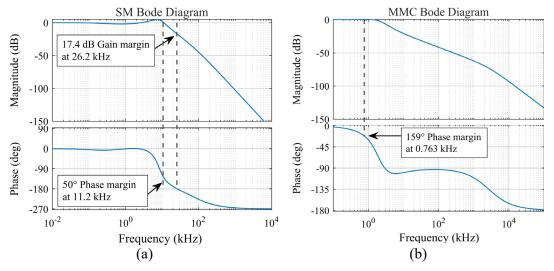

| Fig. 28 Closed loop transfer function for: (a) SM using a type-III controller and (b)                                                    |      |

| MMC using a PI controller.                                                                                                               | 70   |

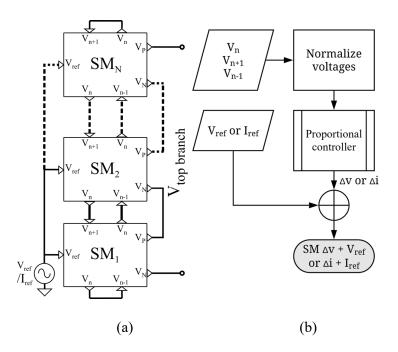

| Fig. 29 MMC (a) branch detailed interconnection, and (b) proportional controller of                                                      | •    |

| each SM to achieve the self-balancing capability.                                                                                        | 73   |

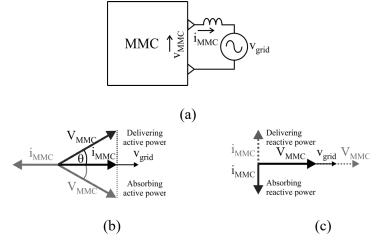

| Fig. 30 MMC connected to the grid: (a) basic diagram, (b) phasors when MMC is                                                            |      |

| delivering or absorbing active power, and (c) reactive power                                                                             | 75   |

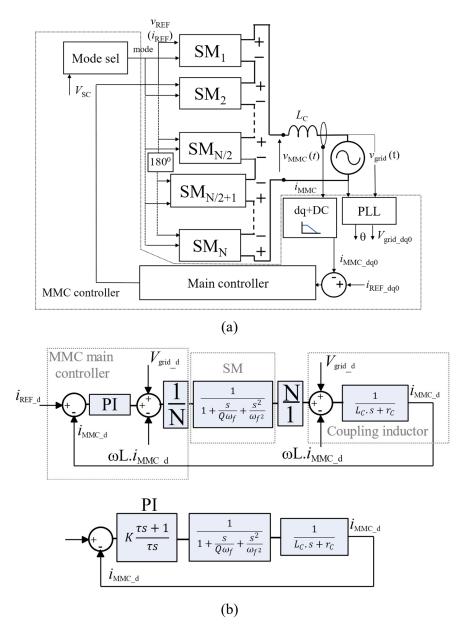

| Fig. 31 MMC controller (a) general scheme, (b) detail of d-component loop                                                                | 76   |

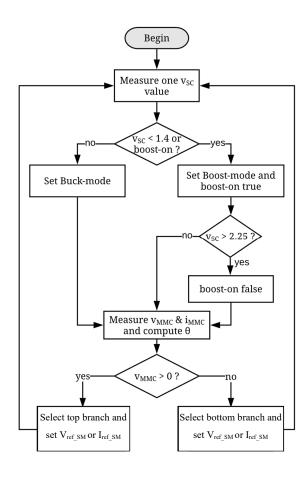

| Fig. 32 MMC control diagram for the mode selection.                                     | 78  |

|-----------------------------------------------------------------------------------------|-----|

| Fig. 33 Buck-mode: (a) balancing process discharging at 10 kW, (b) delivering or        |     |

| absorbing active or reactive power and (c) changing from boost-mode to buck-            |     |

| mode                                                                                    | 82  |

| Fig. 34 Extension for a three-phase system: (a) balanced and (b) non-balanced           | 83  |

| Fig. 35 Internal Buck-Boost balancing system, Case 4 example.                           | 84  |

| Fig. 36 MMC discharging cycle flow diagram for any Case.                                | 89  |

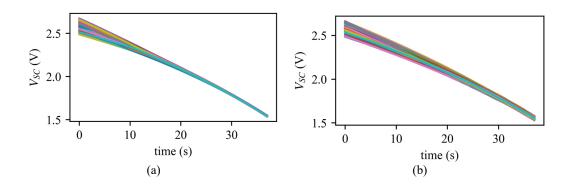

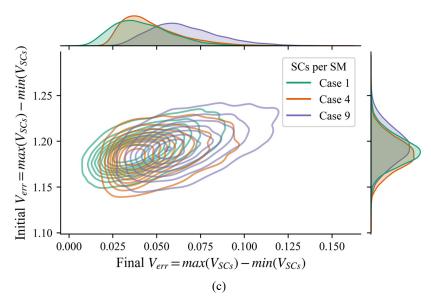

| Fig. 37 Voltage plot of each SC for the discharging cycle for (a) Case 1, (b) Case 4, a | nd  |

| (c) scattered surface plot for Case 1, 4, and 9                                         | 94  |

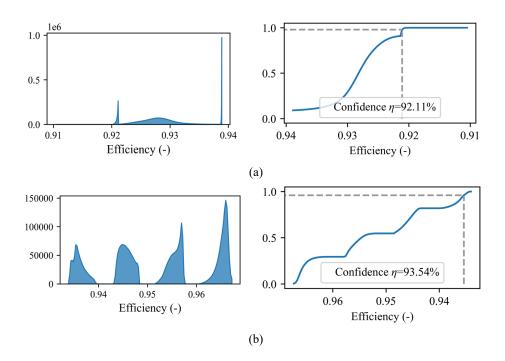

| Fig. 38 SM efficiency histograms and CDF plots for Cases 1, 4, and 9.                   | 96  |

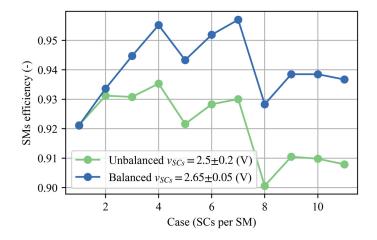

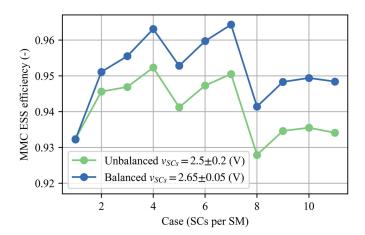

| Fig. 39 Minimum SM efficiency with a confidence level of 95% for unbalanced and         |     |

| balanced initial conditions for all Cases.                                              | 96  |

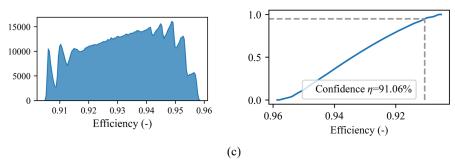

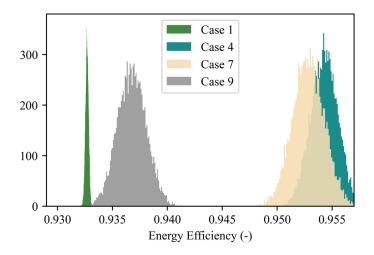

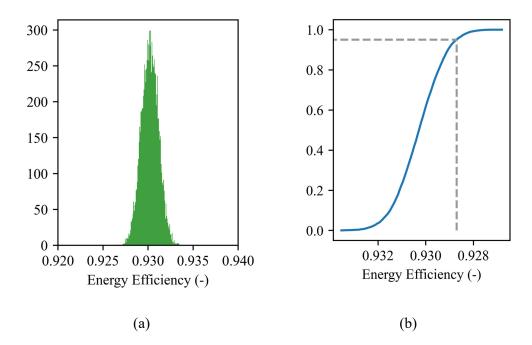

| Fig. 40 Energy efficiency histograms for Cases 1, 4, and 9.                             | 97  |

| Fig. 41 CDF Energy Efficiency plot for (a) unbalanced and (b) balanced initial          |     |

| conditions for all Cases.                                                               | 98  |

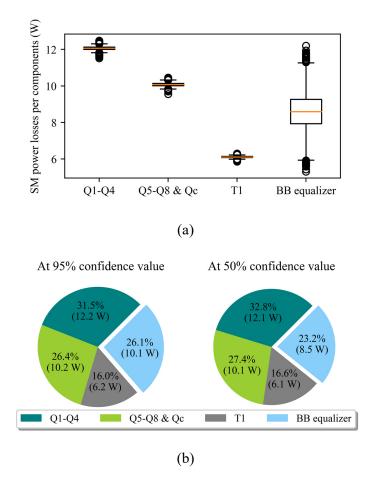

| Fig. 42 SM power losses for the main components (a) box plot and (b) pie charts at 93   | 5%  |

| and 50% confidence levels.                                                              | 100 |

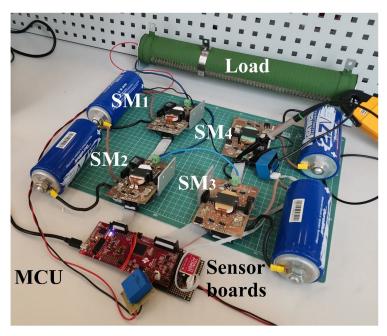

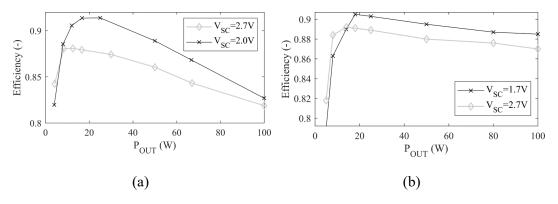

| Fig. 43 Complete MMC Prototype.                                                         | 102 |

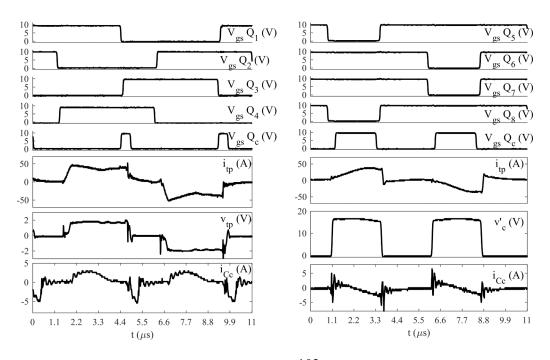

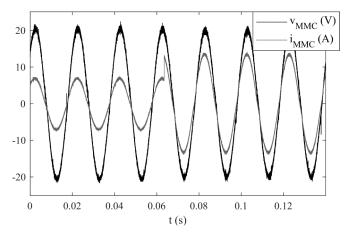

| Fig. 44 Experimental waveforms for each SM in (a) buck and (b) boost-mode               | 103 |

| Fig. 45 MMC output voltage and current for a step change in the load                    | 103 |

| Fig. 46 Step response from (a) R to RL and (b) R to RC.                                 | 104 |

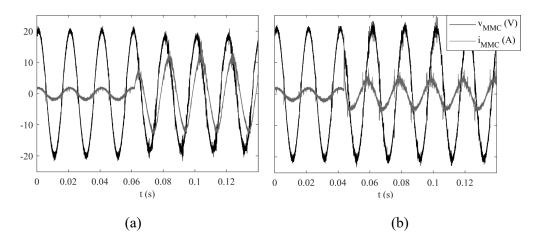

| Fig. 47 Efficiency of the MMC for (a) buck and (b) boost-mode.                          | 104 |

| Fig. 48 MMC (a) prototype with Case 3 SMs and (b) discharge process using initial      |     |

|----------------------------------------------------------------------------------------|-----|

| unbalanced conditions                                                                  | 107 |

| Fig. 49 SM obtained efficiency values vs theoretical curve                             | 109 |

| Fig. 50 Probabilistic study based on the extracted SM efficiency from the prototype, ( | (a) |

| histogram and (b) CDF plot.                                                            | 109 |

| Fig. 51 Four-quadrant plot for bidirectional DC/AC inverters                           | 113 |

| Fig. 52 Capacitor-clamped 3-level DC/AC multi-level inverter                           | 114 |

| Fig. 53 Diode-clamped 3-level DC/AC multi-level inverter                               | 115 |

| Fig. 54 Generalized multi-level DC/AC inverter with P2 cell                            | 116 |

| Fig. 55 Modular Multilevel Converter, (a) basic block diagram, (b) half-bridge SM ar   | ıd, |

| (c) full-bridge SM                                                                     | 118 |

# **List of Tables**

| Table 1. Simulation components for MMC-based ESSs [73].                 | . 47 |

|-------------------------------------------------------------------------|------|

| Table 2. Comparison results and main aspects of each MMC-based ESS [73] | . 51 |

| Table 3. Performance Index results.                                     | . 51 |

| Table 4. Simulation main components                                     | . 80 |

| Table 5. Simulation components of each test case                        | . 91 |

| Table 6. Experimental validation of SM components                       | 106  |

### 1. Introduction

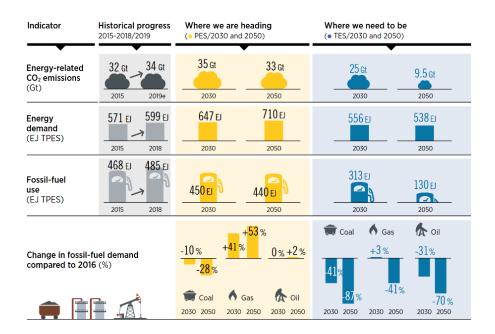

In 2019 renewable energy generation expanded more than electricity demand, resulting in a decrease in fossil-fuel electricity generation, achieving a never-seen scenario [1]. Even though we are facing the post-pandemic economic havoc that COVID-19 caused us, we must continue supporting the integration of renewables into the grid globally. The tendency to increase annual renewable capacity additions is an encouraging development [2], but it is not enough to reduce our dependency on fossil fuels and control CO<sub>2</sub> emissions. Fig. 1 shows the International Renewable Energy Agency (IRENA) forecast and required future scenarios in fossil-fuel energy demand.

Fig. 1 IRENA's forecast for fossil-fuel energy demand and CO<sub>2</sub> emissions [1].

To meet the Paris Agreement of reducing by 70% the carbon emissions and 64% demand for fossil fuels, renewable energy among solar and wind are the more promising ones. However, they come with a challenge for the electric energy industry, their

stochastic behavior. For this reason, several new technologies have to be developed, including electricity storage, namely Energy Storage Systems (ESSs), electric vehicles, smart appliances, and meters [1], [3].

### 1.1. Why ESSs are needed, application examples

ESSs will become a standard for any grid operator since these types of systems would allow the further integration of Variable Renewable Energy (VRE). For today's standards, Flexible AC Transmission Systems (FACTS) devices are widely implemented by grid operators to extend and increase the power transfer capability of the transmission lines and provide a stable supply for consumers. ESSs are the evolution of the Static Synchronous Compensator (STATCOM) FACTS devices by allowing a bigger shift in time or capacity of the generated power when required and still maintaining a stable supply for the consumers [4].

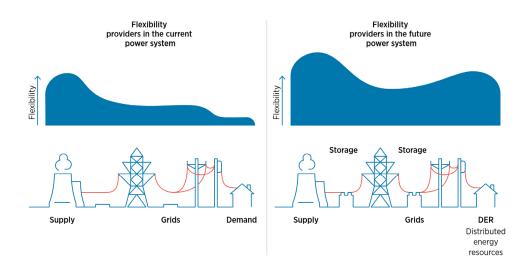

Therefore, the grid will require the addition of the ESSs at different points of the grid, for example before the transmission lines, through the distribution grid, and at the consumer side (residential or commercial) as Fig. 2 illustrates. This will increase the flexibility of the grid and still maintain a stable supply [3], [5].

Fig. 2 Traditional grid vs. emerging flexible grid [6].

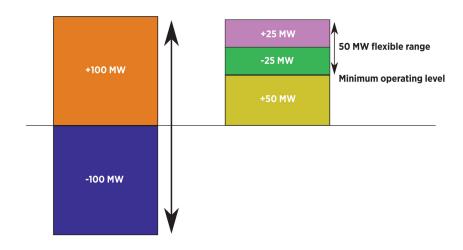

This flexibility cannot be provided by the actual grid because the generators in the power plants cannot be commanded to abruptly change from delivering full power to zero power or vice versa, as they have slow reaction times and initialization sequences that must be met. ESSs on the other hand can accurately and quickly ramp the power output or absorption and therefore compensate for the deviations in the grid as shown in Fig. 3.

Fig. 3 100MW ESS (left) versus 100MW gas turbine (right) [5].

The power handling capabilities of any ESS are determined by the type of storage device used and the power electronic circuitry. The storage device capacity dictates the time of operation as well as the allowed peak power and in most of the cases the circuitry has the same peak power handling capability. Therefore, the design of any ESS is a process that requires understanding the principles of operation of the storage device and optimizing the circuitry for it. This thesis's main contributions are in creating an optimized energy conversion circuitry for the ESS.

### 1.2. Types of energy storage devices and systems

Currently, multiple technologies can provide the required electricity storage. They vary from thermal, electro-mechanical, electro-magnetic, and electro-chemical forms.

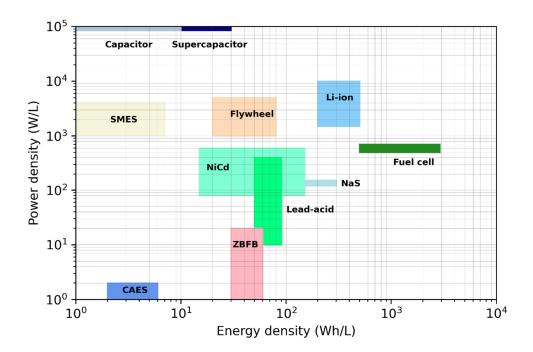

In the form of thermal storage, the most exploited is molten salt [3], [7]. In the electro-mechanical form, we have two types, Compressed Air Energy Storage (CAES) and flywheels [8], [9]. In the form of electromagnetic, we have Superconducting Magnetic Energy Storage (SMES) [4], [8]. And finally, in the electrochemical form of storage, we have lithium-ion, sodium-based, redox flow, lead-acid batteries, and capacitors and supercapacitors [7], [10].

There are many parameters involved in the aforementioned energy storage devices, but two of them are relevant when comparing each device, their power density and their energy density. Fig. 4 shows the comparison between the different types of energy storage technologies [3].

Fig. 4 Energy density and power density comparison between various energy storage devices [3].

Based on Fig. 4 it is possible to infer that if we move in a diagonal from the left bottom to the upper right the volume would start to decrease, and therefore the technologies that can be found in the corner are the most promising ones. However, other considerations have to be taken into account, like cost, durability, and maintenance.

Depending on the application, the energy storage device must be selected based on a techno-economic analysis that considers all the parameters involved, for such reason there is no ideal energy storage device, and some authors started to analyze the combination of them for creating a hybrid ESS.

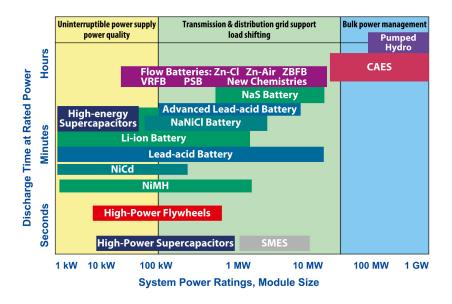

IRENA as well as other authors have identified the most suitable energy storage devices based on the application or the function it will perform in the grid [3], [11]. Which

could be for improving the power quality, transmission, and distribution grid support load shifting and bulk power management. Fig. 5 shows the comparison.

Fig. 5 Energy storage devices are ordered based on their power rating and discharging times, and their possible application in the grid [3].

Supercapacitors (SCs) are energy storage devices with the highest power density relative to Li-ion batteries, flywheels, fuel cells, and superconducting magnetic energy storage systems [8], [10]. Therefore, they are very suitable for maintaining the power quality in the grid for some time in the seconds range.

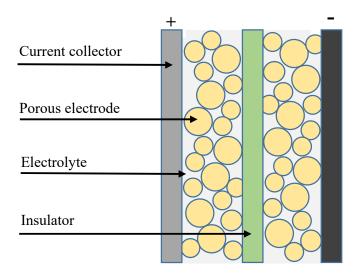

Although SC technology is still developing, the basic principle of storing energy in an SC is through physically separating positive and negative charges as in a normal capacitor. The main difference between a capacitor relies on the porous electrodes that hold the charges, and between those porous electrodes, there is an insulator placed in the middle of both positive and negative plates [10]. Fig. 6 shows the composition of a single SC cell.

Fig. 6 SC single cell composition.

This high-power density comes with a cost, namely that SCs are usually low-voltage devices, around 2.5V to 3.0V maximum [12]. This problem can be overcome by using series connections with passive or active balancing systems, the latter being more efficient [13], [14]. However, in terms of design, this added circuitry creates a more complex and expensive ESS that is also susceptible to failure because of the many parts involved in the system [15], [16].

Moreover, as they behave as a normal capacitor, their Energy capacity E is defined as:

$$E = \frac{1}{2}CV_{MAX}^2,\tag{1}$$

therefore, if we want to use around 75% of its energy capacity the voltage range would have to vary from [V<sub>MAX</sub>/2, V<sub>MAX</sub>]. This creates another limitation in which the power converter has to operate efficiently in the entire voltage range.

Typical applications of SC-based ESSs are related to fast energy injection [17]. For example, in isolated microgrids with a high penetration of renewables [18], SCs maintain the power balance between consumption and generation, because inertia mechanisms are limited.

A review of multiple SC-based ESSs for microgrid applications is presented in [19]. In 2018, 29 out of the 985 electrochemical projects were based on SCs, and the total power of these projects was 34.273 MW. The reviewed ESSs provide 5 top services such as voltage support, transportation services, electric energy time shift, frequency regulation, and renewables capacity firming. Other cases are transmission support, ramping, and load following.

Supercapacitors can provide an alternative to spinning reserves for frequency regulation services [20]. Hence, SC-based ESSs are a suitable offer for grid ancillary services since they have the required high-power energy storage for short periods [21], [22].

Other authors have studied incorporating SCs in low-voltage MMC, for example, for railway traction systems in which each SC is integrated into every Submodule (SM), but only studied analytically [23]. Another SC Low-voltage MMC application was also studied in STATCOMs by incorporating the ESS into the MMC, however, it was only possible by adding a DC/DC converter [24]. The same occurs for a power traction converter, adding SCs as temporary energy storage with an additional DC/DC converter [25].

#### 1.3. ESS grid synchronization

The majority of energy storage devices can only store or convert energy in the form of DC, thus it is not possible to directly interconnect them to the AC grid. Therefore, several subsystems have to be implemented in the ESS to accomplish the so-called grid synchronization.

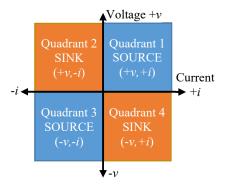

This requires a DC/AC inverter and complex controller circuitry that it is supervising constantly the power flow from DC to AC and the voltage in both AC and DC sides. If the 4-quadrant operation is required, then the circuitry has to be able to adjust active and reactive power as well.

For any type of ESS or inverter-based system, there are two forms of operating the DC/AC inverter: grid-following or grid-forming converter control [26]–[29]. Being the grid-following control the most used in Photovoltaic (PV) and wind inverters in today's applications. The grid-forming control is under development and only a description of how it should operate or behave was introduced in [30]. The description presented of both controls is extracted from [26]:

In a grid-following inverter, the current injected by the inverter to the grid is controlled with a specific phase shift from the grid voltage at the Point of Common Coupling (PCC). Thus, the fundamental frequency phasor of the grid voltage is needed at any time for the precise calculation of the inverter's reference current, whose amplitude and angle concerning the grid voltage phasor are properly modified by the outer controllers to inject the required amount of active and reactive power or control the Root Mean Square (RMS) voltage.

In a grid-forming inverter, the magnitude and angle of the voltage at the PCC are controlled by the inverter. Hence, the fundamental frequency phasor of the grid voltage at the point of connection is not strictly necessary to be known. Based on the type of network to which the inverter is connected, an isolated system or a slack bus, it is possible to adapt the injected instantaneous active and reactive power using additional outer controller loops, to provide voltage and frequency support. In an isolated system, a grid-forming inverter could behave itself like a slack bus. When connected with other power sources, through an inductive line, the grid-forming inverter controls the active power by adjusting the angle. The voltage magnitude is independent of the active power control.

Since ESSs already have the required energy buffer to fully operate in the gridforming control, they can also be used to provide frequency support and black start services.

Many authors have proposed grid-following algorithms that have proven to allow the rapid expansion of renewables integration to the grid [31]–[33]. However, if we want to continue the further penetration of renewables into the grid, authors have started to study the impact of the many inverters with rigid control schemes based on grid-following. Alerting the problems that could arise under this phenomenon [30], [34].

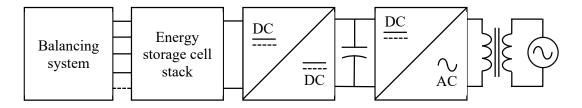

#### 1.4. The basic elements of ESSs

An ESS needs to keep the energy storage devices or cells balanced, protect them from overvoltage, and create the output voltage using bidirectional DC/DC to provide a stable voltage for the DC/AC inverter. A basic ESS is composed of a balancing system (if the cells cannot exceed their capacity/voltage rating), the energy storage devices or

cells, a bidirectional DC/DC converter, a DC link capacitor, and a bidirectional DC/AC converter, as Fig. 7 shows [17], [35].

Fig. 7 ESS basic block diagram.

The balancing system must be selected depending on the technology used for storing the energy. For any lithium-based battery it is important to always keep the battery cells balanced, and if there is a necessity to correctly measure the State of Charge (SOC), then instead of using only a balancing system it is necessary to include a Battery Management System (BMS). Which can supervise the cell's voltages, currents, and temperature for an extra layer of protection, allowing the BMS to protect the cells from overcharge, over-discharge, over-current, or short-circuit [36].

The same concept of using a BMS applies to any battery technology that has to keep voltage and current levels within a certain range. For example, this is also true for lead-acid batteries, although they can withstand or tolerate the overcharge condition in comparison to lithium batteries, they will start to degrade faster if the cells are not properly matched.

If another type of technology is used and there is a necessity to supervise various parameters of the device, then a more general Energy Management System (EMS) has to be implemented. For example, for flywheels, it is necessary to measure the rotor speed and the moment of inertia. In CAES the parameters are pressure, volume, temperature,

and discharge profile. Therefore, the EMS will behave differently depending on the energy storage technology implemented [37].

For SCs, the simplest approach is to guarantee that the cell stack is voltage-balanced, resulting in a balancing system that only needs to measure the voltage of each cell and then balance the cells accordingly. If a passive system is used, the most used method is to slowly discharge the overcharged SC cell. However, the passive method will waste the excess energy in the form of heat, which increases the temperature of the stack if there is no proper heat dissipation. Therefore, although the active method is more complex, it is the most suitable since the excess of energy from one overcharged SC cell is transferred to another one, with efficiencies ranging from 70 to 90%. If there is a necessity to supervise the SOC of the SC stack and other parameters, then a Supercapacitor Management System (SMS) has to be implemented. Many authors have proposed different methods to analyze the SOC of the SCs, the main goal is to fit all the physically measured data into a model to accurately determine the SOC [38].

Mainly, SC voltage changes linearly with the state of charge, so a DC/DC converter with a wide input voltage range and a constant DC output voltage is commonly needed [39]. A DC link connects the DC/DC converter to a traditional DC/AC converter, which creates an AC signal. In addition, galvanic isolation is important when the ESSs are connected to the grid to avoid stray currents or DC currents. A bulky 50Hz transformer must be used if none of the other stages has isolation, which increases the converter's size. Each of these circuits or stages requires a careful design process to accomplish the power budget.

#### 1.5. Objective of the research and structure

In a traditional SC-based ESS, four stages are needed: the energy storage devices, the balancing system, and the DC/DC and DC/AC converters that connect the storage devices to the grid. Being the main source of losses the DC/DC and DC/AC converters. Since all the energy will flow from the SC cells to the AC grid across these converters or vice versa. If each stage has an efficiency of up to ~97%, the total efficiency for the whole ESS will be ~94%. The main contribution of the proposal is an SC-based ESS which reduces the number of stages by adopting the Modular Multilevel Converter (MMC). Thus, it is possible to create an ESS with increased efficiency since fewer losses from the stages are present and this single-stage efficiency will determine the whole MMC-based ESS's efficiency.

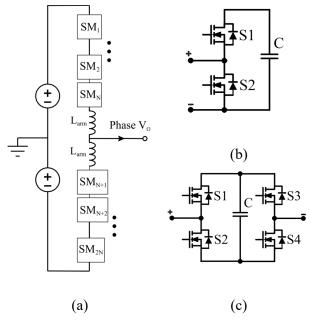

Instead of the traditional approach, the MMC can be used, which is based on a high-voltage DC source and a series of submodules (SMs). In this system, the DC/DC and DC/AC conversions are performed in the SMs, which consist of DC/DC converters. These MMC topologies have been used in High Voltage Direct-Current (HVDC) transmission lines [40], [41]. The main advantages of MMCs are the simplicity in scaling up the voltage of the system by adding more SMs to the MMC, transformerless operation, straightforward implementation for redundancy and fault tolerant operation, the superior quality of the output waveforms and the usage of standard components for each SM [42], [43]. The Appendix provides a reference to the multi-level inverters and the MMC basic SM cells.

The relevant aspect of this research is to integrate a single or a few SCs in each of the SMs, and therefore, no high-voltage DC source is needed. In addition, each SM works in a voltage range of a few volts, which allows the use of low-voltage switches, with low conduction losses [23] and makes possible a low Total Harmonic Distortion (THD) of the AC output voltage and current. Chapter 2 presents the state-of-art of high-gain bidirectional DC/DC converters, bidirectional multi-level converters, and MMC-based ESS.

The research addresses the design methodology of the proposed MMC-based ESS for low-voltage applications (120~480 VAC), the selection of a proper DC/DC bidirectional topology for each SM, the internal SM voltage/energy balancing problem, the grid synchronization, and the ability to inject or absorb active and reactive power from the grid efficiently. In Chapter 3, simulations are done using Matlab Simulink and LTSpice or HSpice, Python, and Numba library for highly intensive CPU simulations.

For the experimental part, multiple PCBs were designed and fabricated at the Skoltech Power Electronics lab, and the testing of the prototypes required high-current measurement probes. Demonstrating with a fully operational small-scale prototype the ability to perform the self-balancing process and the DC/DC and DC/AC conversions in a single stage by adopting the MMC topology for Low-Voltage energy sources as the SCs. Hence, the novelty resides in the selection, and design of the power converters and the proposed techniques to use them as balancers, DC/DC, and DC/AC converters simultaneously. Saving size, reducing cost, and increasing the flexibility or modularity of ESSs. In Chapter Chapter 4, shows the experimental tests done to validate the proposed strategy and ESS. The results are a real working prototype with great efficiency using standard silicon semiconductor MOSFETs and could be further improved by using silicon carbide or gallium nitride MOSFETs.

### **Chapter 2. Literature Review**

Most ESS have an interface between the energy storage device and the grid or microgrid, which is the DC/DC converter. Depending on how the energy storage device operates the DC/DC converter has to be suitable for extracting the most energy of it, and with great efficiency in both directions. Therefore, the DC/DC converter must be designed to operate in the range of voltages and power levels required by the energy storage device. Normally, for stationary applications in the grid or microgrid, there is no constrain in the volume of the converter, but if the ESS is implemented for mobile or vehicle applications, then this also has to be taken into account, as well as the total heat dissipation of the ESS.

This chapter is devoted to giving an overview of the state-of-the-art DC/DC converters and DC/AC inverters developed for ESS applications. Since the proposed ESS uses SCs as energy storage devices the constraints for the DC/DC converter are mainly that they need to be wide input voltage range, high power handling, bidirectional power flow, and high efficiency.

Many authors have presented different techniques to accomplish the wide input voltage range, one of the basic principles is to use various cascaded stages to obtain a stable voltage output. The first stage elevates the voltage to a certain level using a boost converter topology, and then, the subsequent stages are in charge of regulating the voltage to a suitable level for the DC/AC inverter.

In this chapter, several types of topologies for DC/DC converters and DC/AC inverters are covered, namely, high-gain DC/DC converters, bidirectional multi-level

converters, MMC-based ESSs and their basic SMs topologies, and finally, a comparative of actual ESSs, their efficiencies, costs, Total Harmonic Distortion (THD) and volume.

#### 2.1. High-gain DC/DC converters

High-gain DC/DC converters are of special importance if the energy storage device operates at a low-voltage level. As discussed in the previous chapter, it is possible to place the energy storage devices in series to increase the voltage, but if they cannot surpass a certain voltage level or rating, then it is mandatory to introduce a balancing system. However, if too many cells are placed in series, the complexity of the balancing system will increase too. Therefore, this is the reason for implementing a high-gain DC/DC converter which can boost the voltage from the energy storage stack to the desired levels to use with the DC/AC inverter. For example, off-grid inverters boost the 48V input voltage from lithium or lead-acid batteries to 400V so the DC/AC inverter can operate at 220 or 230VAC levels.

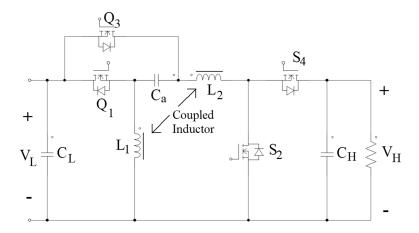

Authors in [44] presented a high-gain bidirectional quadratic DC/DC based on a coupled inductor with current ripple reduction capability. By using the coupled inductor, the converter can operate in both power flow modes with a reduced ripple current at both input and output ports. The voltage gain for the boost mode is as high as two cascaded boost converters, and the same applies to the buck mode, hence a high gain is achieved. The authors analyzed in detail the operation in continuous conduction mode, discontinuous conduction mode as well as the boundary conditions. The prototype of 250W with a low side voltage of 27V was able to boost it to 110V in the high side output. The efficiency achieved by the prototype stayed above 90% for both boost mode and buck-mode, in a wide range of power variations.

Fig. 8 High-gain bidirectional quadratic DC–DC converter based on coupled inductor [44].

In [45], the authors have presented a wide input range DC/DC converter suitable for fuel cells, this circuit was also tested with commercial SC modules inserted before T<sub>1</sub>, at the input side. The presented converter was able to take an input voltage of 42-60V and provide a stable output voltage of 400V with a maximum power of 5kW. A two-stage approach was used, The first stage is a three-level boost converter cascaded with the second stage, a current-fed two-inductor boost converter topology, which has a higher voltage gain and provides galvanic isolation from the input source. The first stage was designed to boost the voltage from the wide input of 42-60V to 80V, so the cascaded stage works always in its optimal voltage input in terms of efficiency. A total efficiency of 92% was achieved with the converter. Fig. 9 shows the wide input range DC/DC converter presented by the authors.

Fig. 9 Wide input range DC/DC converter composed of two cascaded stages [45].

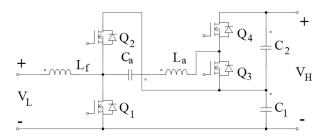

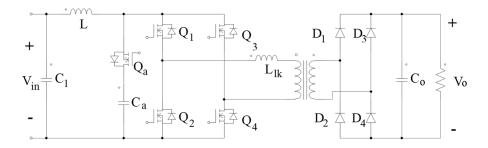

In [46], the authors presented a new converter by combining two half-bridges, and the resulting converter along with a novel PWM plus phase-shift control can operate with high-gain and soft-switching characteristics. Fig. 10 shows the presented converter, C<sub>a</sub> is used to couple the two half-bridges, and V<sub>H</sub> is the sum of the output voltage of the first bridge plus the output voltage of the second bridge. The built 3kW prototype was able to convert from a high side voltage of 450V down to 86V, achieving efficiencies values greater than 96% in both power flows. Since the converter can achieve Zero Voltage Switching (ZVS) at all load and voltage conditions and in both power flows, high efficiency is maintained for wide operating power. However, the main drawback of this converter is that V<sub>L</sub> and V<sub>H</sub> are not isolated.

Fig. 10 High-gain soft-switching bidirectional DC/DC converter composed of two half-bridges [46].

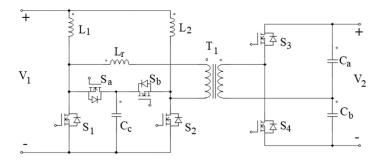

In [47], a ZVS Bidirectional DC/DC converter with a phase-shift plus PWM control scheme is presented. The novelty relies on solving the drawbacks of the current-voltage-fed bidirectional DC/DC converter, which are high voltage spikes and high circulating conduction losses. This was accomplished by adding an active clamp branch (Cc, Sa, and Sb), and the phase-shift plus PWM control technique, therefore all the switches can achieve ZVS in a wide range of load variation and input and output voltages variations too. The 1.5kW prototype was able to achieve a voltage conversion with an input voltage varying from 22 to 32 V and obtaining a regulated voltage of 270V with efficiencies up to 90%. Additionally, this converter provides isolation due to the High Frequency (HF) transformer T<sub>1</sub>. Fig. 11 shows the converter's schematic.

Fig. 11 ZVS bidirectional DC/DC converter with phase-shift plus PWM control scheme [47].

In [48], a high-gain dual-input converter is presented, which allows the connection of different types of energy storage devices to create a hybrid ESS. The converter is bidirectional, therefore is possible to extract/storage energy with a specific energy storage device, Hence a full-active configuration is achieved. With only two control signals is possible to select from which voltage source or energy storage device to extract the energy or store it. Also, few components are needed, and because it does not use HF transformers there are no voltage spikes or recirculating currents. The authors suggested the use of a Li-ion battery for bulk energy storage and SCs for delivering power. The converter can achieve a high gain at its output port with a quadratic expression  $V_0 = V_{SC}/(1 - D_2)^2$ . The built prototype was able to achieve 94% at 200W transferring power from the second input (Vsc) to the output. Fig. 12 shows the converter's schematic.

Fig. 12 High-gain dual-input DC/DC converter [48].

In [49], the authors presented a full-bridge with an active clamp and the controller can achieve ZVS in a wide input voltage range. Although initially studied in [50], the authors made a complete analysis of the boost-mode operation of the converter. The results were validated with a prototype that was able to boost the voltage from a varying input voltage of 22-41V to 350V at the output. In addition, they verified experimentally the ZVS operation through a wide input voltage range and power loads, achieving an efficiency of 94% with a 500W-rated prototype. Fig. 13 shows the converter's schematic, the active clamp is composed of Qa and Ca. Although the authors only analyzed the boost-mode, in [50] the buck-mode is also analyzed, therefore the converter can be bidirectional and suitable for ESSs.

Fig. 13 Extended range ZVS active-clamped current-fed full-bridge isolated DC/DC converter [49].

As seen from the literature review, the techniques that allow the implementation of high-gain converters with great efficiency are the techniques of ZVS intervals and HF transformers to increase the gain even further. Moreover, the converter has to be able to operate efficiently if a wide-input range is required, or in other words, be able to regulate or work on all the possible duty cycle selections.

Based on the presented converters it is possible to categorize them and select an adequate DC/DC converter for a specific application, other considerations have to be taken into account like control complexity, cost, the estimated resulting volume of the converter, and so on. Traditional ESS designers select the DC/DC converter that allows them to extract the maximum energy from the energy storage device and can be paired with the DC/AC inverter too.

One limiting factor of high-gain DC/DC converters is the need to properly size the MOSFET or IGBT breakdown voltage. Commercial Silicon (Si) MOSFETs are widely available from voltage ranges up to 4.7kV, however, the tradeoff would be the increased R<sub>DS</sub>(ON) value, which could lead to high conduction losses, this also applies to Silicon Carbide (SiC) MOSFETs and IGBTs. Therefore, if high voltage gain ratios are needed to reach voltage levels that are beyond the capabilities of the switches another type of topology must be selected. The next subsection focuses on a solution for the described limitations.

### 2.2. Bidirectional multi-level converters

As discussed in the previous subsection, one limiting factor of any traditional DC/DC converter topology is the voltage breakdown of the MOSFET or IGBT. One solution is to put the MOSFET or IGBTs in series and switch them exactly at the same time to share the total voltage across the switches. However, this solution would require complex circuitry that can synchronize the switching operation and might be not so practical. Therefore, a different technique is used to share the voltage across the switches without the problems of synchronization mismatch. This can be done by using multi-level converters.

Multi-level converters are key for reaching higher voltage levels by using lower voltage rating MOSFETs or IGBTs. Although the first application of a multi-level converter was in the field of an inverter motor controller [51], the idea of synthesizing a higher voltage waveform from various voltage sources remains. Moreover, if the number of levels or stages increases it is possible to reduce the THD as each step transition will be closer to the desired output waveform. This is explained in the Appendix, and in this subsection, a survey of bidirectional DC/DC multi-level converters is presented. Hence, the main benefit of using this approach is the possibility of reaching higher voltages by placing a series combination of lower-rating MOSFETs, capacitors, and diodes. Thus, the efficiency can be increased as the device is not handling the total voltage as in a traditional DC/DC converter, and the switching losses can be reduced as well.

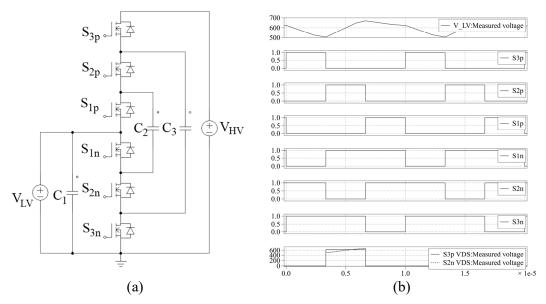

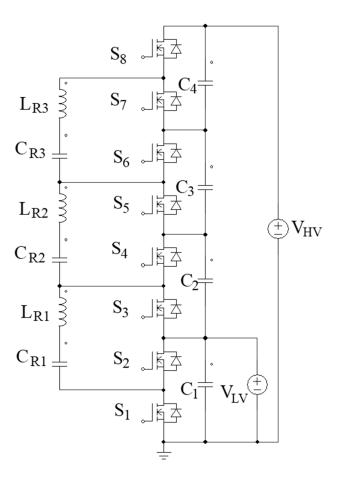

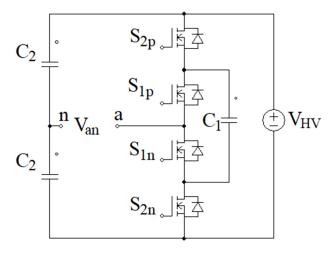

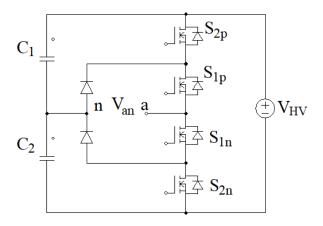

Traditionally, two types of multi-level converters started to be of great importance for DC/DC power conversion, the flying capacitor and the diode-clamped converters. The conventional topology for a flying capacitor multi-level DC/DC converter is presented in Fig. 14.a, composed of only 3 levels or stages. For example, the converter can transfer power from a low-voltage power source V<sub>LV</sub> to a high-voltage source V<sub>HV</sub>. However, the switching scheme is dependent on the number of stages or levels used. In this 3-level example, the switching pattern for a 50kHz multi-level converter with an input voltage of 2000VDC and an output voltage of around 520VDC is presented in Fig. 14.b. Notice that the duty cycle of S<sub>1p</sub> to S<sub>3p</sub> is only 1/3, if more levels are added to decrease the output voltage then the duty cycle is limited to 1/n. Therefore, in practice, not so many levels can be used. But the advantage is that the MOSFETs are not directly connected to the total input voltage and only a proportion of the voltage is "seen" through the MOSFET,

in this example the Drain-Source Voltage (VDS) for both S<sub>3p</sub> and S<sub>2n</sub> remains below 700VDC.

Fig. 14 Flying-capacitor multi-level DC/DC converter, 3-level example.

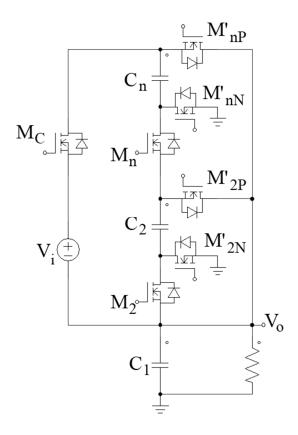

In [52], one of the first multi-level switched-capacitor DC/DC converter analyses is presented, if MOSFETs are used instead of diodes bidirectional power flow can be accomplished. The authors detailed that because there are no magnetic components involved, therefore the converter can be easily implemented for monolithic integration. Fig. 15 shows the converter, notice that the basic block is composed of three MOSFETs ( $M_n$ ,  $M'_{nP}$ , and  $M'_{nN}$ ) and only one capacitor  $C_n$ . Depending on the n number of stages it is possible to create a converter with a  $V_o = V_i$ .n. Although the converter is old and uses many active elements, the analysis presented, and the novelty relies on the technique, which can be used for different types of switched-capacitor DC/DC converter topologies.

Fig. 15 An n-stage switched-capacitor DC/DC converter schematic.

In [53], the authors propose an improvement to the previous flying capacitor multi-level DC/DC converter. Interestingly, using the same topology from Fig. 15 and only changing the switching states they were able to achieve better power conversion ratio and less voltage ripple. They also validated the converter for bidirectional operation. The feasibility of the converter was verified through simulations and with a prototype of 6-stages. The prototype was able to transfer power from V<sub>i</sub> at 80V to V<sub>o</sub> at 12V, it was able to achieve a maximum power conversion of 120W with an efficiency of around 93%. However, the authors mention that the efficiency can be increased by properly selecting the MOSFETs with a good value of R<sub>DS</sub>(ON).

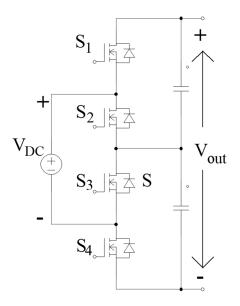

In [54], a bidirectional multi-level DC/DC converter is presented, the converter uses no magnetic components and can change the voltage output almost continuously. Since there are no magnetic components, the converter can work under higher temperature conditions. Although in reality, it would be impossible to switch a capacitor due to the high transient currents that can be reached, the authors take advantage of the parasitic inductance of the cable and the Equivalent Series Inductance (ESL) of the capacitor on the battery side to limit the current and therefore avoid an overcurrent condition in the MOSFETs that could damage them. The article shows how the converter operates and the authors validated the converter with a prototype that was able to increase the input voltage V<sub>DC</sub> two times to V<sub>out</sub>. The prototype achieved high-efficiency values, higher than 98%, through the entire power load from 1kW to almost 11kW.

Fig. 16 Multi-level bidirectional DC/DC converter with high efficiency.

In [55] a SiC-based bidirectional multi-level high-voltage gain switched-capacitor resonant converter is presented. The converter is based on the same principle of multilevel

topologies and therefore it can achieve reduced voltage stresses on the switches, high voltage gains, and bidirectional conversion ability. Furthermore, the converter transfers energy via the capacitors, hence the weight of the converter is reduced in comparison to inductive-based ones. The authors presented a four-level prototype that was able to reach a V<sub>HV</sub> of 2kV and 500VDC at V<sub>LV</sub>, using SiC transistors for increased efficiency and power ratings. The prototype was able to reach up to 5kW and efficiencies higher than 97%. Since four levels were used, the V<sub>DS</sub> for the MOSFETs will not exceed 650VDC, allowing to use of Si or SiC MOSFETs in that range. Fig. 17 shows the schematic for the four-level resonant multi-level converter.

Fig. 17 SiC-based high-gain bidirectional DC/DC multi-level resonant converter.

As demonstrated by the authors, multi-level converters possess many advantages for creating DC/DC converters with reduced voltage stresses on the switches, and as seen from some of the presented converters, they can create output waveforms with low distortion. However, one disadvantage is the increased number of gate-drive circuits that have to be interfaced relatively to each MOSFET. Therefore, if many levels or stages are required to reach a specific high-voltage level, the many gate signals can be the limiting factor to escalate the converter, or reliability can be a concern due to the many circuits involved.

Based on the generalized multi-level topology other authors started to develop new topologies by modifying the basic cell arrangement, adding new features like ZVS [56]–[58], or increasing the degree of control for the output waveform with different control techniques [59]–[61].

The benefits in low-voltage applications of multi-level topologies are the reduced switching losses if the number of stages is properly selected [62]. The authors addressed how to select the correct number of stages [62], [63].

As can be seen from the multi-level topologies, the main drawback is that by increasing the number of levels there is also an increase in components number, for a desired number of levels (L) would need a transistor (Q) count Q = (L)(L-1). Therefore, each level increase supposes a cost increase and an efficiency decrease as more energy will be dissipated through the many transistors if they are not properly selected. These drawbacks have been already addressed and now authors focus their attention on Modular Multilevel Converters.

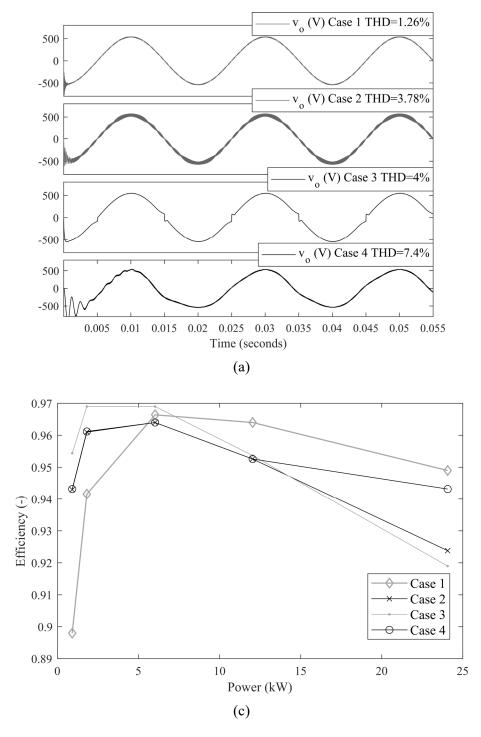

## 2.3. MMC-based Energy Storage Systems

MMCs have been deeply studied for High-Voltage DC (HVDC) energy transmission applications. Even though it is an expensive technology, the benefits of implementing it in large-scale projects turn them a viable solution in contrast with traditional AC transmission lines, as they provide a more robust and efficient way to transfer energy along long distances [41], [64]–[66]. In comparison to other types of topologies used for HVDC [67], [68], MMCs can be escalated as the requirements for HVDC lines increase by simply adding more SMs. MMC low-voltage applications started to develop and this entire subsection is devoted to comparing different MMC-based ESSs.

As the MMC technology matures, authors started to research the possibility of using MMCs as the interface between energy storage devices and the grid, this allows the creation of an ESS capable of achieving all the advantages that MMC possess, and mainly for straightforwardly allowing the implementation of ESSs at low-voltage or medium-voltage levels. Several authors have presented multiple topologies based on MMC to incorporate SCs as the main energy device, due to the increased cycle life in comparison to batteries and because SCs can fulfill the high-power requirement, useful for grid operators to sustain the power quality of the grid as shown in Fig. 5. Another application is in power traction converters and by adding supercapacitors, kinetic energy can be recovered from the motor within the same converter [25]. For these reasons, this literature review will mainly cover SCs as the main energy device, and only MMC topologies that are intended for incorporating an energy storage device. A review and comparison of newer advanced SM cells can be found in [69].

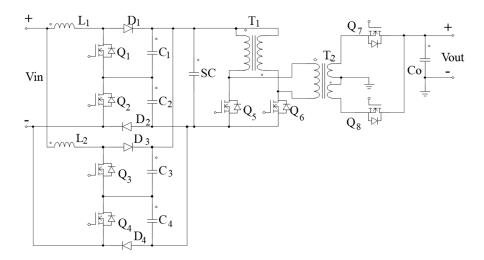

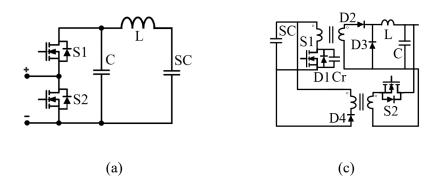

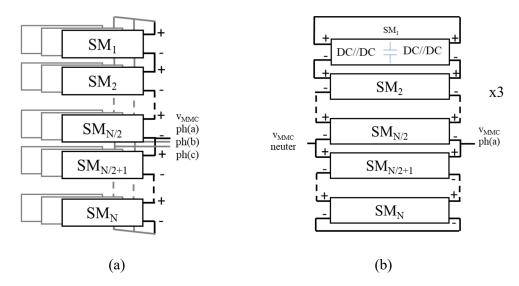

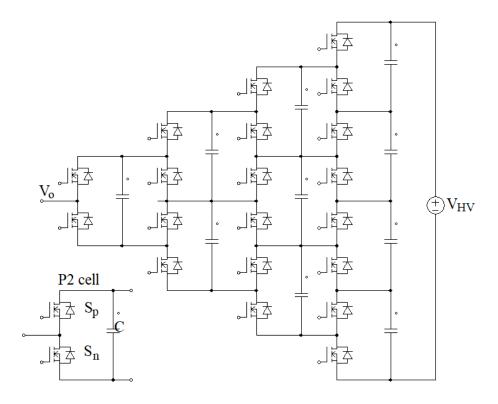

SCs can be added by integrating them into the SMs as presented in [70], [71]. Most authors have chosen to modify the basic SM cell variant, the half-bridge structure, to incorporate the SC as the energy storage device (Fig. 18.a and Fig. 18.b). From Fig. 18.a, it can be seen that the half-bridge SM has a lower transistor count. However, as the SM works as a two-level block: the output is either the capacitor voltage or zero. Due to that, if the SM voltage is high, many SCs (or capacitors) must be introduced in series. However, this would create a more complex SM as it will require a balancing system for each of them. Hence this topology is limited in terms of the maximum voltage in each SM. However, if the quantity of SMs is high, the Total Harmonic Distortion (THD) will remain low. Fig. 18.b presents a solution for the aforementioned limitations of the cell shown in Fig. 18.a, by including a boost DC/DC converter as an interface to the SC, thus it is possible to achieve higher voltage levels in each SM as there is no limitation from the SC voltage rating. The drawback is the increased number count of transistors and their controller; although intended for motor operation, the ESS control scheme is described in [25]. In addition, the efficiency of the DC/DC boost converter could impact the overall efficiency of the ESS as this converter is a hard-switch topology.

If efficiency is a critical factor, an SM with soft-switching capabilities can be used, at the cost of involving a more complex controller [42]. This can be done by redefining the SM cell to take advantage of soft-switching techniques to increase the effective power absorbed or injected from the SC. This more complex SM is shown in Fig. 18.c. The SM cell benefits from the soft-switching techniques and a high efficiency could be achieved easily in contrast with the previous SM cells from Fig. 18.a and Fig. 18.b. Furthermore, instead of increasing the transistor count, this topology uses diodes and a transformer to

achieve a high voltage conversion ratio, thus is possible to use a single SC per SM. The major drawback is the complexity of the controller for each SM.

Finally, other authors have created a hybrid ESS by incorporating the SCs at the DC-link level by rearranging the complete MMC topology and interconnecting the SCs through DC/DC converters [72]. Instead of modifying the SM cell, the energy storage device is connected at the DC-link level as shown in Fig. 18.d. Here, the controller needed to operate each of the DC/DC converters is simpler in comparison to all the previously described SM cells as only a single reference is needed and thus, a single PI controller could achieve the voltage regulation of the DC-link level. The drawback is the increased count of elements needed to achieve the same operation as the other compared topologies. Also, as originally presented in [72], the SM cell can incorporate a different type of energy storage device like a battery, and thus a hybrid ESS could be created.

Fig. 18 (a) Half-bridge with SC connected through an inductor, (b) Half-bridge with integrated DC/DC boost converter, (c) Soft-switching SM cell, and (d) Alternative MMC topology to include SCs.

# 2.4. Comparison of MMC-based ESSs (efficiencies, costs, THD, and volume)

Based on the MMC-based ESSs presented in the previous subsection, a comparison study was presented in [73]. This study recovers quantitative information from each ESS, such as THD, efficiency, SMs needed, transistor count, diode count, inductors, controller complexity, and costs. To make a fair comparison, the only energy storage device used was SCs. Table 1 shows the components used for extracting with numerical simulations the THD and efficiencies for each MMC-based ESS shown in Fig. 18. To refer to each one of the MMC-Based ESS a Case number is used further on.

**Table 1.** Simulation components for MMC-based ESSs [73].

| Component | Fig. 18.a [70], [71]<br>– Case 1 | Fig. 18.b [25] –<br>Case 2 | Fig. 18.c [42] –<br>Case 3 | Fig. 18.d [72] –<br>Case 4 |

|-----------|----------------------------------|----------------------------|----------------------------|----------------------------|

| $L_{arm}$ | 1.2mH                            | 1.2mH                      | 2.4mH                      | 1.2mH                      |

| C         | 100uF                            | 240uF                      | 1000uF                     | 200uF                      |

| L                             | 1uH                  | 10uH                   | 2.4uH                   | N/A                    |

|-------------------------------|----------------------|------------------------|-------------------------|------------------------|

| SC                            | 137F                 | 166F                   | 137F                    | 137F                   |

| SC Model                      | XLM-62R1137A-<br>R   | XLR-48R6167-R          | XLM-62R1137A-<br>R      | XLM-62R1137A-<br>R     |

| Cycle life                    | 1,000,000            | 1,000,000              | 1,000,000               | 1,000,000              |

| # of SMs                      | 20                   | 12                     | 10                      | 12                     |

| Voltage per SM                | 57V                  | 95V                    | 114V                    | 95V                    |

| $f_{sw}$                      | 20kHz                | 20kHz                  | 35kHz                   | 20kHz                  |

| S1 to S4 Model                | IPP050N10NF2S        | 2xIPP075N15N3G         | 2xIPB107N20N3           | 2xIPP075N15N3G         |

| S1 to S4 Max $V_{DS}$         | 100V                 | 150V                   | 200V                    | 150V                   |

| S1 to S4 R <sub>DS</sub> (ON) | $5~\mathrm{m}\Omega$ | $7.5~\mathrm{m}\Omega$ | $10.7~\mathrm{m}\Omega$ | $7.5~\mathrm{m}\Omega$ |

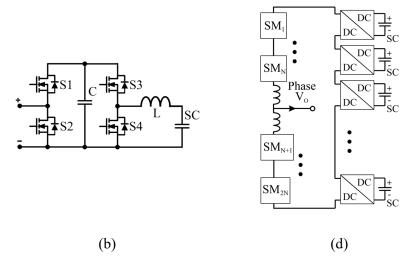

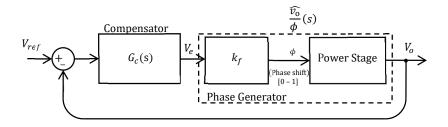

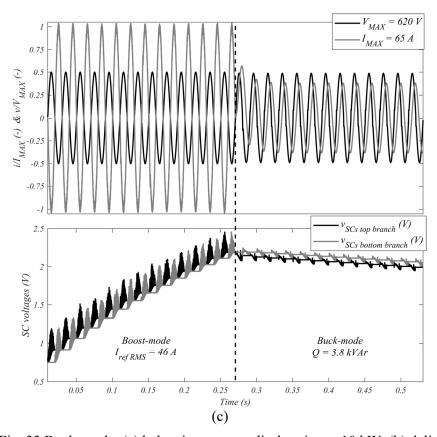

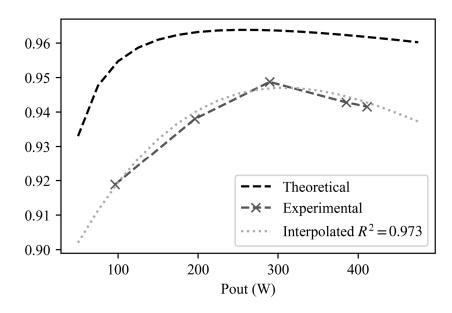

The numerical simulations were done using PSIM software, the first test was configured to extract the THD of a sinusoidal waveform for further comparison between the topologies. Fig. 19.a shows the resulting output voltage waveforms with the THD calculated for each case. Case 1 exhibits a better performance in terms of THD as it has an increased number of SMs, thus more voltage steps are developed and therefore better envelops the AC reference. Although Case 2 has a lower THD than Case 4 or Case 3, it can be appreciated as a high-frequency component due to the DC/DC boost converters switching, a possible solution would be to only increase the  $f_{sw}$  of the DC/DC boost converter, but this results in a more complex controller inside each SM.

Fig. 19 MMC-based ESS comparison results for (a) Output voltage and calculated THD and (b) Efficiencies.

The second test bench addresses another important aspect of ESSs, the efficiency of the whole system. To accomplish this objective, multiple simulations were done, varying the requested output power. Since PSIM only calculates the conduction losses caused by the ON state voltage drop across the switches, to include the switching losses in the case of hard-switching events, as the ones in Cases 1,2 and 4, those power losses were calculated considering the currents and voltages in the switches at the commutation instant in a spreadsheet and subtracted from the obtained values of the simulations. The results are shown in Fig. 19.b.

Finally, a comparison table was built using the extracted parameters from the MMC-based ESSs, Table 2 shows the results for each Case. With these results, we create a Performance Index (PI) function to aid in selecting the best Case for a particular desired application. A linear cost function with weighted coefficients was used to evaluate each case:

$$PI = k_{cost} \cdot \frac{c}{c_{NOM}} + k_{weight} \cdot \frac{w}{w_{NOM}} + k_{vol} \cdot \frac{v}{v_{NOM}} + k_{SM} \cdot \frac{SM}{SM_{NOM}} + k_{eff} \cdot \frac{100\%}{eff} + k_{THD} \cdot \frac{THD}{THD_{NOM}},$$

$$(2)$$

where  $k_{cost}$ ,  $k_{weight}$ ,  $k_{vol}$ ,  $k_{SM}$ ,  $k_{eff}$ , and  $k_{THD}$  are the coefficient that depends on the application where the sum of all of them is one, and c, w, v, SM, eff and THD are the cost ( $k_VA$ ), weight, volume, number of SMs, efficiency, and THD of each case which are normalized with the nominal values.

Three applications were evaluated using the proposed PI function: Gridconnected, vehicular or mobile, and Uninterruptible Power Supply (UPS) or off-grid applications. Table 3 shows the values for all of the cases. Case 1 offers a simple circuit with low THD. This is a good solution for grid-connected applications, due to the increased number of SMs and because in this particular application, there is no penalty in the PI cost function for having more SMs. Moving to vehicular applications, in which the volume, weight, and total number of SMs are important, Case 3 is better suited, largely benefiting from the reduced number of SMs. If more efficiency is required, more transistors can be added in parallel, although this will further increase the cost of the system. Finally, for the UPS or off-grid application, both Case 1 and Case 3 are recommended, and as aforementioned, if high efficiency is a must, Case 3 can be improved by adding more transistors in parallel. However, if the system cost has to be further reduced, then Case 1 is the most suited.

**Table 2.** Comparison results and main aspects of each MMC-based ESS [73].

| Case | THD   | Efficiency | SMs<br>needed | S  | D | L                       | Controller complexity | Cost |

|------|-------|------------|---------------|----|---|-------------------------|-----------------------|------|

| 1    | 1.26% | 94.9%      | High          | 2  | 0 | 1                       | Low                   | +    |

| 2    | 3.78% | 92.4%      | Medium        | 4  | 0 | 1                       | Medium                | ++   |

| 3    | 4%    | 91.9%      | Low           | 2  | 3 | 1 and 2<br>Transformers | High                  | +++  |

| 4    | 7.4%  | 94.3%      | High*         | 4* | 0 | 2*                      | Low                   | ++   |

<sup>\*</sup>Considering the extra DC/DC converters at DC-link.

**Table 3.** Performance Index results.

| Application         | Case 1 | Case 2 | Case 3 | Case 4 |

|---------------------|--------|--------|--------|--------|

| Grid-connected      | 2.28   | 2.96   | 2.74   | 3.17   |

| Vehicular or mobile | 4.15   | 4.68   | 4.03   | 4.47   |

| UPS or off-grid     | 2.55   | 2.89   | 2.55   | 2.83   |

However, from the analyzed MMC-based ESSs there is the drawback of involving an additional outer loop balancing controller for both Case 1 and Case 3 to balance the

energy storage devices, hence this supposes an extra computational cost besides the algorithm that it is in charge of from sorting out the SMs that should be connected or bypassed. In addition, for Case 1 there is the necessity of using many SMs, and if these SMs incorporate a single cell of low-voltage energy storage devices such as SCs then the large number of SMs could lead to an unviable solution for medium-voltage grid interconnections. Case 3 solves this problem by using an HF transformer to increase the voltage as desired by using a higher turn-ratio, however, it still involves using a low-frequency switch to select which arm is connected to the grid, which could be difficult to implement in higher voltage levels. The next chapter describes the proposed MMC which can overcome these problems, and the SC balancing algorithm is embedded in each SM, hence scalability complexity is removed.

# Chapter 3. Proposed MMC

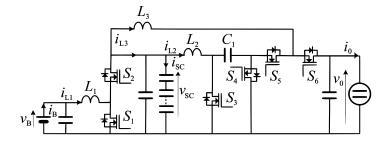

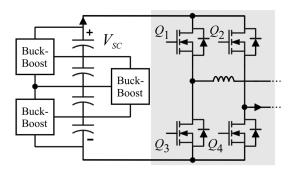

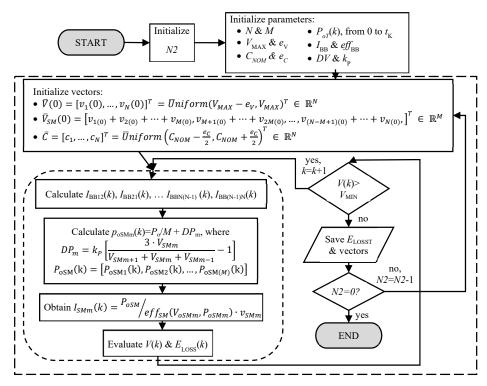

Instead of the traditional approach from Fig. 20, a Modular Multilevel Converter (MMC) can be used as the authors presented in the previous chapter for low-voltage ESSs. In this system, the DC/DC and DC/AC conversions are performed in the SMs, and the active balancing system can be performed with the proposed self-balancing technique embedded in each SM. As mentioned in the previous chapter, these MMC topologies have been used in High voltage DC transmission [40], [41]. One of the main advantages of MMCs is the simplicity in scaling up the voltage of the system by adding more SMs to the MMC [42], as Fig. 21.a shows for a traditional MMC topology. However, for low-voltage applications, the benefit of adding more SMs allows for a further increase in the energy storage capacity of the system or the power handling by placing more SMs in parallel.

Fig. 20 ESS basic block diagram.

The proposed MMC shown in Fig. 21.b is used to extract the energy from supercapacitors and to create a chain of voltage sources based on bidirectional DC/DC converters. The implemented submodule is a bidirectional full-bridge topology [49], [50], [74], [75]. This circuit was selected because of its straightforward use, ease of control, high efficiency, and galvanic isolation through an HF transformer. In the proposed ESS, the energy is not extracted from a high-voltage DC source, but it is rather obtained from

a single SC or an SC stack which is included in the submodule. Thus, the submodules contain the energy storage device and they are bidirectional.

Fig. 21 Block diagram (a) of the traditional and (b) the proposed MMC topology.

Along with the contributions of this research is the development of an ESS based on an MMC which can perform the functions of balancing, DC/DC and DC/AC conversions and storage in a single block, resulting in a modular converter that is easily expandable at higher voltages with an efficiency similar to traditional ESSs. In addition, this new approach based on MMC can be further improved to have an efficiency that is higher than the traditional topologies using wide-band semiconductors and parallel techniques.

## 3.1. Principle of operation

As described in the previous chapter, the SM is based on a well-known DC/DC converter which was selected due to its characteristics of good efficiency, bidirectional, isolation, and ease of control and implementation. Fig. 22 shows the schematic of the

selected DC/DC converter. This is a soft-switching converter that has galvanic isolation provided by transformer  $T_1$  and uses synchronous rectification and an active clamp ( $C_c$ ,  $Q_c$ ) to reduce the voltage stress in the switches.

Fig. 22 Bidirectional full-bridge DC/DC converter, presented in [50].

Since the MMC has to operate in both power flow directions with high efficiency, the selected converter has to be addressed in both directions. The converter has two modes of operation, namely, Buck-mode and Boost-mode. In the Boost-mode, power flows from the inductor  $L_1$  endpoint to the SCs, thus the active bridge is  $Q_5$ - $Q_8$ . In the Buck-mode power flows from the SC to  $L_1$ .

The SC is connected in the voltage-fed section part and the output port is in the current-fed section. This allows wide output voltage regulation, which is necessary to operate with a half-bridge rectified sinusoidal output voltage per leg. The drawback is the increase in the switches' current stress in comparison with the arrangement where the ports are interchanged, that is, the SC in the current-fed section and the output in the voltage-fed section. The circuit will be analyzed in both power flow operation modes in the following subsections.

# 3.1.1 Buck-mode ( $V_{SC} \rightarrow V_O$ )

The circuit is analyzed by taking five-time intervals (from  $t_1$  to  $t_6$ ) in one half of a switching period (Ts), as shown in Fig. 24.a. For this buck-mode, the proposed controller for the gating signals is shown in Fig. 23 and the main waveforms are presented in Fig. 24.a. Before the first-time interval (before  $t_1$ ),  $Q_1$  and  $Q_2$  are on, and  $Q_3$ ,  $Q_4$  and  $Q_c$  are off (Fig. 24.b). This means that the voltage in the transformer's primary winding is zero ( $v_{tp}$ =0). The 2<sup>nd</sup> bridge ( $Q_5$ - $Q_8$ ) is conducting. The diodes from  $Q_5$ - $Q_8$  are on, and the synchronous rectifier is working, so the transformer's secondary voltage ( $v_{ts}$ ) is zero volts and  $v_c$ =0, too. Therefore, no current is flowing from the primary to the secondary winding of the transformer ( $i_{Llk}$ = $i_{ts}$ =0). The inductor current ( $i_{L1}$ ) flows through the 2<sup>nd</sup> bridge and the load. Because  $v_c$ ' is zero, so  $i_{Ce}$ =0. This initial condition is the last time interval of the previous half-cycle.

Fig. 23 Proposed SM Buck-mode controller with gating signals.

Fig. 24 Bidirectional full-bridge, (a) waveforms, (b) before 1<sup>st</sup> interval, (c) 1<sup>st</sup> interval, (d) 2<sup>nd</sup> interval, (e) 3<sup>rd</sup> interval, (f) 4<sup>th</sup> interval, and (g) 5<sup>th</sup> interval for the Buckmode.

In the 1<sup>st</sup> time interval (Fig. 24.c),  $[t_1, t_2]$ ,  $Q_1$  and  $Q_4$  are on,  $Q_2$ ,  $Q_3$  and  $Q_c$  are off, and  $v_{Llk}$ =- $V_{tp}$ = $V_{SC}$ . Notice that as  $i_{Llk}(t_1)$ =0, at zero current  $Q_2$  turns off and  $Q_4$  turns on; thus, both transitions occur at soft switching.  $v_{ts}$ =0 because the  $i_{L1}$  is still flowing through the 2<sup>nd</sup> bridge diodes from  $Q_5$ - $Q_8$ . This interval is equivalent to the off-time in the continuous mode for a buck converter, so the inductor current follows:

$$i_{L1}(t) = i_{L1}(t_1) - \frac{V_0}{L_1}(t - t_0),$$

(3)

because v'<sub>c</sub>=0, and this is valid from t<sub>1</sub> to t<sub>2</sub>. i<sub>Llk</sub> continues increasing until the current in the secondary winding reaches i<sub>L1</sub> and Q<sub>6</sub> and Q<sub>7</sub> turn off. Therefore, for the 1<sup>st</sup> time interval:

$$V_{sc} = L_{lk} \frac{di_{Llk}}{dt},\tag{4.a}$$

and

$$i_{Lk} = i_{L_{lk}}(t_0) - \frac{V_{SC}}{L_k}(t - t_1).$$

((4.b)

The time interval ends when  $i_{Llk}(t_2)=n.i_{L1}(t_2)$ , where n is the turns ratio of  $T_1$ . At that moment, the  $2^{nd}$  time interval starts  $[t_2, t_3]$  (Fig. 24.d).  $Q_2$ ,  $Q_3$ , and  $Q_C$  are still off and  $Q_1$  and  $Q_4$  are still on (so there are no switching transitions between the  $1^{st}$  and  $2^{nd}$

intervals). Q<sub>6</sub> and Q<sub>7</sub> are already off, and v'<sub>c</sub> starts increasing. The equations that govern the  $2^{nd}$  time interval are (considering  $L_{mag} >> L_{lk}$ ):

$$V_{sc} - \frac{v'_c}{n} = L_{lk} \frac{di_{L_{lk}}}{dt}$$

(5.a)

$$v'_{c} - V_{o} = L_{1} \frac{di_{L_{1}}}{dt}$$

(5.b)

$$i_{Cc} = C_c \frac{dv'_c}{dt} \tag{5.c}$$

$$\frac{i_{lk}}{n} - i_{Cc} = i_{L_1} \tag{5.d}$$

and the solution is:

$$\frac{di_{L_{lk}}}{dt} = \left[ \left( \frac{V_{sc}}{L_{lk}} - \frac{V_{sc}}{L_{lk} + \frac{L_1}{n^2}} \right) + \frac{\frac{V_o}{n}}{L_{lk} + \frac{L_1}{n^2}} \right] cos(\omega_0 t) + \frac{V_{sc} - V_o}{L_{lk} n^2 + \frac{L_1}{n}}$$

(6.a)

where the resonant frequency is  $\omega_0 = \left[ C_c \left( \frac{n^2 L_{lk} L_1}{n^2 L_{lk} + L_1} \right) \right]^{-1}$ . Considering L<sub>1</sub>>>>n<sup>2</sup>L<sub>lk</sub>, the equation can be approximated to:

$$\frac{di_{L_{lk}}}{dt} \approx \frac{V_{sc}}{L_{lk}} cos(\omega_0 t) + \frac{V_o \cdot n}{L_1} cos(\omega_0 t) + \frac{V_{sc} - \frac{V_o}{n}}{\frac{L_1}{n^2}},$$

(6.b)

and integrating ilk:

$$i_{L_k} \approx \left(\frac{V_{sc}}{\omega_0 L_{lk}} + \frac{V_o \cdot n}{\omega_0 L_1}\right) \sin(\omega_0 t) + \frac{V_{sc} - \frac{V_o}{n}}{\frac{L_1}{n^2}} \cdot t + I_{LMIN} \cdot n,$$

(6.c)

where  $I_{LMIN}=i_{L1}(t=t_2)$ . This time interval ends when v'<sub>c</sub> reaches n.V<sub>SC</sub>. Using (6.c) and (5),  $i_{L1}$  is:

$$i_{L1} = I_{LMIN} + \frac{V_{sc} \cdot n - V_0}{L_1} (t - t_2), \tag{7}$$